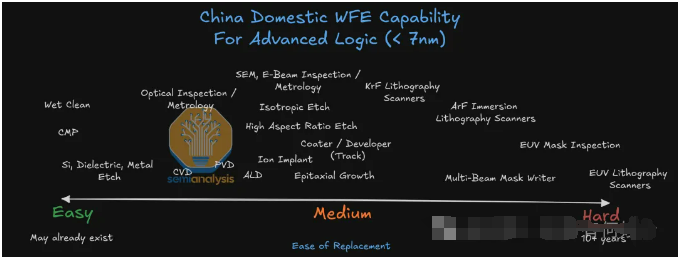

既然三大先进芯片制造商都已经展示了CFETS(complementary field-effect transistors:互补场效应晶体管),那么晶体管密度几乎翻倍的未来处理器的愿景已开始成形。CFET是一种单一结构,堆叠了CMOS逻辑所需的两种类型的晶体管。在本周于旧金山举行的IEEE国际电子器件会议上,英特尔、三星和台积电展示了他们在晶体管的下一代发展方面取得的进展。(四川半导体微组装设备公司)

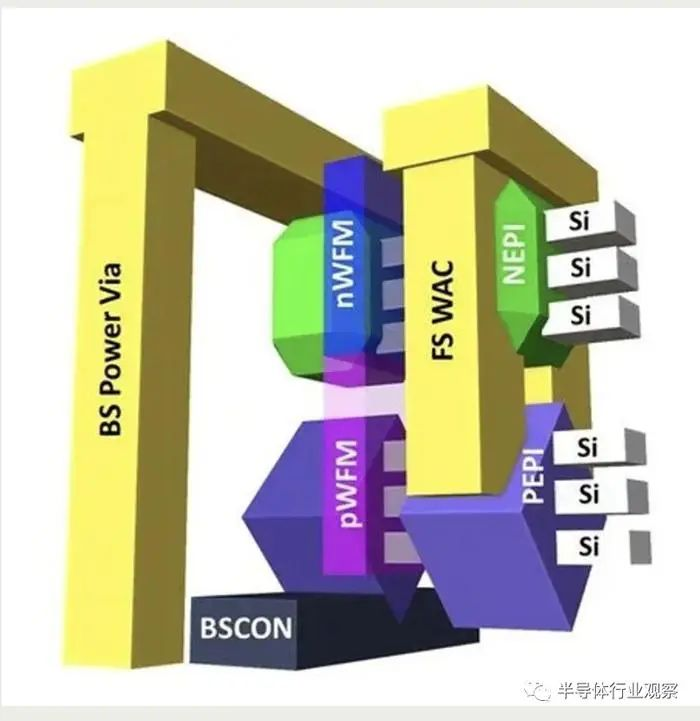

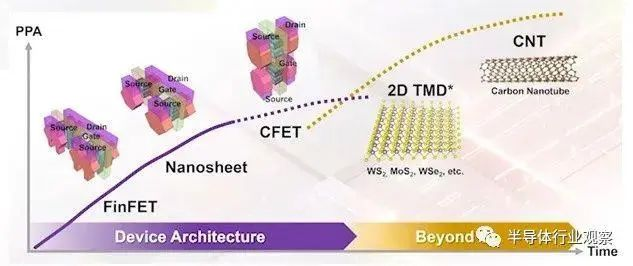

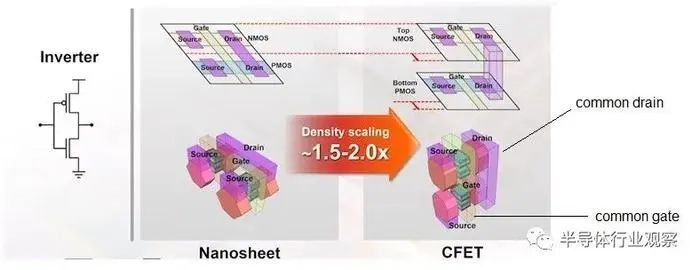

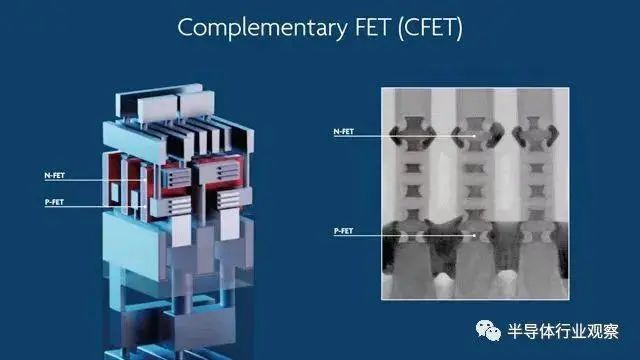

芯片公司正在从2011年以来使用的FinFET器件结构过渡到纳米片或全栅晶体管。这些名称反映了晶体管的基本结构:在FinFET中,栅极控制流过垂直硅鳍的电流;在纳米片器件中,该鳍被切割成一组带(ribbons),每个带都被栅极包围。CFET本质上采用较高的ribbons堆叠,其中一半用于一个器件,一半用于另一个器件。正如英特尔工程师之前所说,该设备在单个集成流程中构建了两种类型的晶体管(nFET和pFET)。

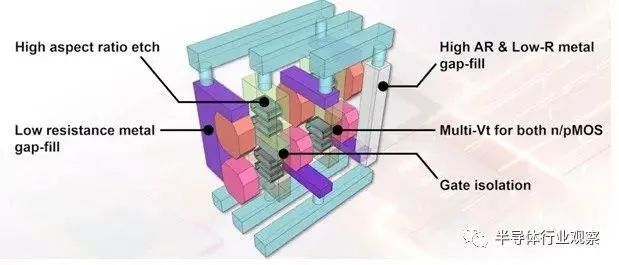

在去年的VLSI技术与电路研讨会上,台积电研发高级副总裁 Y.J。Mii博士也分享了对CFET的看法。如下图所示,CFET工艺保留了环栅纳米片的优点,同时垂直制造pFET和nFET器件。(图中,pFET位于底部,nFET位于顶部。)

在上面描述的反相器逻辑门的横截面中,突出显示了两个器件的公共栅极输入和公共漏极节点。

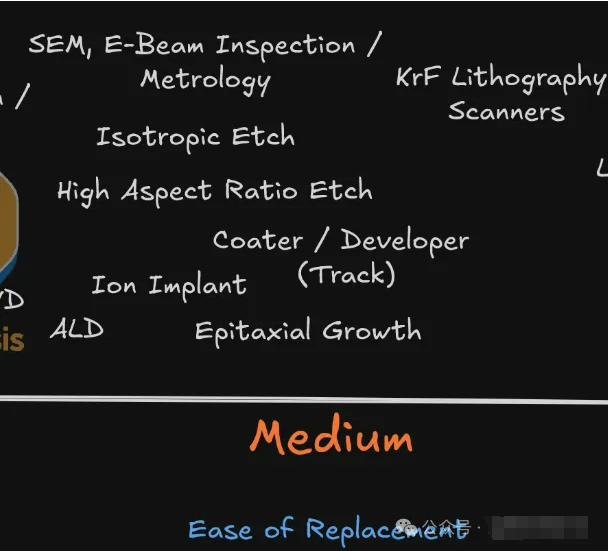

虽然Mii博士没有具体说明,但有关高AR蚀刻和金属填充的评论表明台积电的研发重点是单片CFET工艺技术。(四川成都微组装设备)

CFET,何去何从?

另一种选择是,“顺序”CFET,在不同的晶圆上制造pMOS和nMOS器件,然后使用层转移工艺将两者结合在一起。这两种选择都不容易,但相对于现状来说,两者都有优势。

更多的四川半导体微组装设备资讯请联系:18980821008(张生)19382102018(冯小姐)

四川省微电瑞芯科技有限公司http://www.wdrx-semi.com/